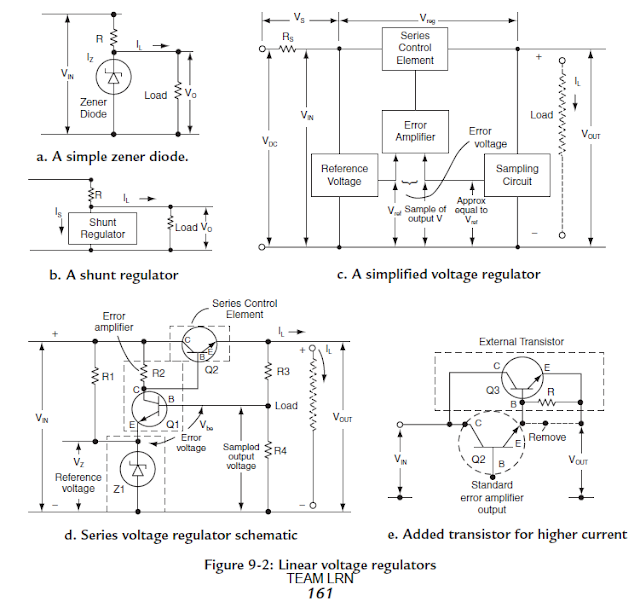

From Figure 9-2c. The input voltage VDC is the voltage out of the rectifier and filter of Figure 9-1.

There is an impedance associated with the rectifier and filter.It is RS shown in Figure 9-2c. As a result, the output voltage, VOUT, is equal to:

VOUT = VDC – ILRS – VREG

= VDC – VS – VREG

= VDC – (VS + VREG)

Using this information, the regulation can be explained as follows: VDC is always considered constant. The regulator varies VREG to keep VOUT constant as IL and VS change. With an increase in IL and thus VS, VOUT would tend to decrease; however, VREG is reduced to compensate and VOUT remains constant. A decrease in IL causes a decrease in VS, but regulation compensates by increasing VREG so that VOUT remains constant. VDC was considered constant but if VDC changes, either up or down, regulation follows to compensate by increasing or decreasing VREG to keep VOUT constant.

Percent Regulation :

The load regulation of a voltage regulator can be expressed as follows (where the load is some specified

current value): % Load Regulation = (Vno load – Vload × 100) / Vload

If Vno load = 11V and, at a specified current, Vload = 10V then

% Load Regulation = (11 –10 × 100) / 10

% Load Regulation = 10%

Common percent load regulation for IC voltage regulators is from 1% to 5%.

Example 2.

Voltage RegulationTo have 1% load regulation for the above supply where VNO LOAD = 11V, at the specified load, what does the VLOAD have to be?

1% = (11 – VLOAD × 100) / VLOAD

0.01 = 11 – VLOAD

VLOAD

VLOAD (1 + 0.01) = 11

VLOAD = 11/ 1.01 = 10.89V.

No comments:

Post a Comment